Sự phát triển của bóng bán dẫn: Từ phẳng đến CFET, Tích hợp 3D xác định lại tiến trình bán dẫn

Trong hơn nửa thế kỷ, ngành công nghiệp bán dẫn đã phát triển nhờ tuân theo một quy tắc đơn giản: làm cho bóng bán dẫn nhỏ hơn.Việc thu nhỏ kích thước tính năng mang lại hiệu suất cao hơn, công suất thấp hơn và chi phí trên mỗi bóng bán dẫn thấp hơn.Nhưng ngày nay, con đường này đã đạt đến giới hạn về mặt vật lý và kinh tế.Kỷ nguyên của việc mở rộng quy mô thuần túy đã kết thúc và một kỷ nguyên mới của đổi mới cấu trúc và tích hợp 3D đã bắt đầu.

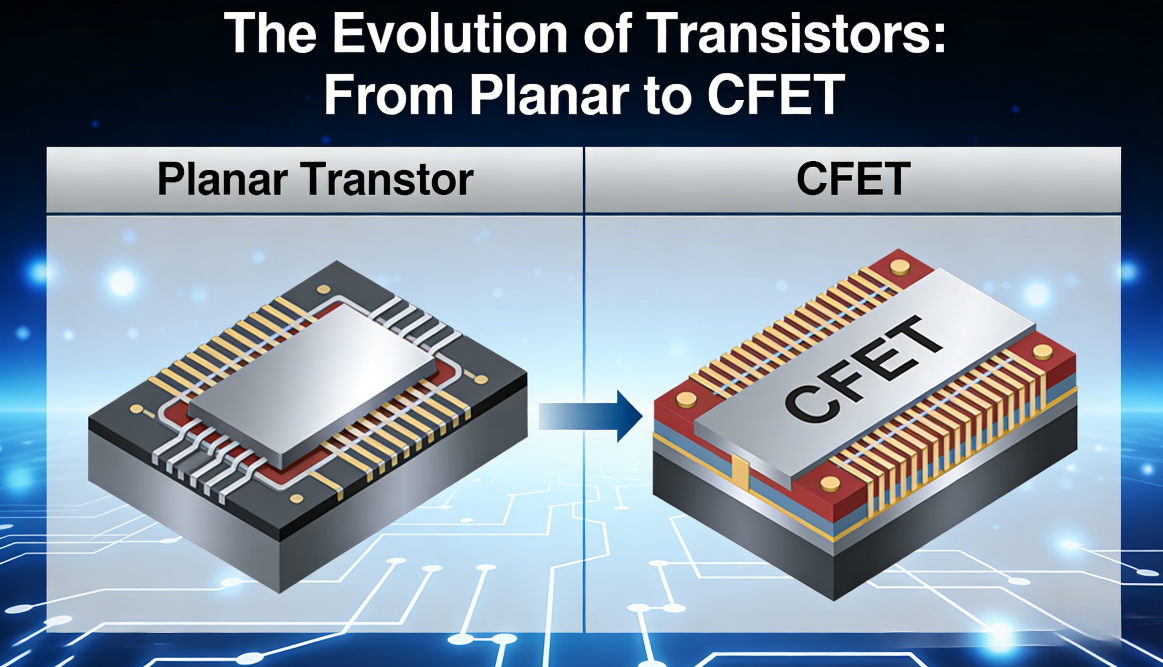

Bản thân bóng bán dẫn đang trải qua một cuộc cách mạng kiến trúc hoàn chỉnh.Từ MOSFET phẳng đến FinFET, từ tấm nano GAA đến xếp chồng CFET, mỗi bước thể hiện sự chuyển đổi từ thu nhỏ sang xây dựng lại bóng bán dẫn trong ba chiều.Đây không chỉ là cải tiến gia tăng—mà còn là sự xác định lại hoàn toàn về cách thức chip mang lại hiệu suất.

Bốn thế hệ kiến trúc bóng bán dẫn

1. Transistor phẳng (2D truyền thống)

Cấu trúc phẳng cổ điển, nơi cổng điều khiển kênh từ trên cao.Nó thống trị ngay từ những ngày đầu cho đến 40nm và 28nm.Khi kích thước bị thu hẹp hơn nữa, dòng điện rò rỉ và kiểm soát tĩnh điện trở thành những vấn đề nan giải.

2. FinFET (Điều khiển cổng 3D)

Kênh trở thành một “vây” thẳng đứng, với cổng bao quanh ba mặt.Điều này cải thiện đáng kể khả năng kiểm soát tĩnh điện, giảm rò rỉ và cho phép thu nhỏ quy mô xuống 7nm, 5nm và thậm chí 3nm.FinFET trở thành nền tảng của kỷ nguyên chip hiệu suất cao hiện đại.

3. GAA Nanosheet (Cổng toàn diện)

Ở mức 2nm trở xuống, FinFET đạt đến giới hạn.GAA thay thế vây bằng các tấm hoặc dây nano nằm ngang xếp chồng lên nhau, được bao quanh hoàn toàn bởi cổng.Nó mang lại khả năng kiểm soát tốt hơn, công suất thấp hơn và dòng điện cao hơn.GAA hiện là cấu trúc chủ đạo cho các chip loại 2nm trên TSMC, Samsung và Intel.

4. CFET (FET bổ sung)

Biên giới tiếp theo: xếp NMOS và PMOS theo chiều dọc.CFET gói hai bóng bán dẫn vào trong một diện tích duy nhất, giúp giảm đáng kể diện tích và cải thiện mật độ.Đây là bước tiến hóa cuối cùng của việc mở rộng quy mô bóng bán dẫn trước khi quá trình tích hợp hệ thống 3D thực sự diễn ra.

Tại sao việc mở rộng quy mô một mình không còn hiệu quả nữa

- Chi phí xử lý tăng theo cấp số nhân tại mỗi nút mới

- Rò rỉ lượng tử và các ràng buộc vật lý làm cứng các giới hạn

- Độ trễ kết nối và mức tiêu thụ điện năng vượt quá tốc độ bóng bán dẫn

- Chip nguyên khối lớn có năng suất thấp và chi phí cao

Ngành công nghiệp đã nhận ra: hiệu suất không còn đến từ các bóng bán dẫn nhỏ hơn nữa.Nó đến từ kết nối tốt hơn, kiến trúc thông minh hơn và tích hợp theo chiều dọc.

Kỷ nguyên mới: Ba lớp đổi mới 3D

Tiến trình bán dẫn hiện được xác định bởi ba chiều của thiết kế 3D:

- Bóng bán dẫn 3D: FinFET, GAA, CFET – xây dựng bóng bán dẫn theo chiều dọc

- Xếp chồng thiết bị 3D: Bộ nhớ logic, liên kết lai, xếp chồng SRAM

- Tích hợp hệ thống 3D: Chiplet, đóng gói 2.5D/3D, tích hợp dựa trên bộ chuyển đổi

Cùng nhau, chúng tạo thành 3D×3D×3D thời đại: bóng bán dẫn, thiết bị và hệ thống đều trở thành ba chiều.

DTCO: Năng lực cốt lõi mới

Khi việc mở rộng quy mô kết thúc, Đồng tối ưu hóa công nghệ thiết kế (DTCO) trở nên quan trọng.Nó có nghĩa là cùng thiết kế kiến trúc, cấu trúc bóng bán dẫn, định tuyến kim loại và đóng gói ngay từ đầu.Những công ty mạnh nhất không còn chỉ là những công ty dẫn đầu về quy trình nữa mà còn là những công ty tích hợp cấp hệ thống.

Hiệu suất đi dây, cung cấp điện, thiết kế tản nhiệt và mật độ băng thông giờ đây quyết định hiệu suất thực của sản phẩm.

AI là động lực tối thượng

AI và điện toán hiệu năng cao đòi hỏi băng thông, hiệu suất năng lượng và mật độ chưa từng có.Những yêu cầu này không thể được đáp ứng bằng cách chia tỷ lệ truyền thống.Họ yêu cầu:

- Kết nối bộ nhớ-điện toán băng thông cực cao

- Hiệu quả năng lượng cực cao cho mỗi hoạt động

- Song song lớn và tích hợp dày đặc

AI đã buộc toàn bộ ngành phải từ bỏ quy mô thuần túy và nắm lấy sự tích hợp không đồng nhất 3D hoàn toàn.

Kết luận: Tương lai không nhỏ hơn mà cao hơn

Thời đại thu hẹp bóng bán dẫn đang mờ dần.Tương lai của chất bán dẫn không phải là làm cho các thiết bị nhỏ hơn mà là xây dựng các hệ thống cao hơn, dày đặc hơn và kết nối thông minh hơn.

Từ Planar đến FinFET đến GAA đến CFET, bóng bán dẫn đã hoàn thành quá trình phát triển của nó.Trận chiến tiếp theo sẽ diễn ra vào Tích hợp 3D, đóng gói tiên tiến và thiết kế cấp hệ thống.Đây là nơi quyết định thập kỷ dẫn đầu về chất bán dẫn tiếp theo.